### 計測自動制御学会東北支部 第 282 回研究集会 (2013.7.17) 資料番号 282-11

## 設計容易性を指向した非同期 FPGA のアーキテクチャ

## Designability-aware Architecture of an Asynchronous FPGA

小松与志也\*,張山昌論\*,亀山充隆\*

Yoshiya Komatsu\*, Masanori Hariyama\*, Michitaka Kameyama\*

#### \*東北大学大学院情報科学研究科

\*Graduate School of Information Sciences, Tohoku University

キーワード: フィールドプログラマブルゲートアレイ (FPGA), 再構成可能 LSI (Reconfigurable LSI), 自己同期式回路 (Self-timed circuit), 非同期式回路 (Asynchronous circuit)

連絡先: 〒980-8579 仙台市青葉区荒巻字青葉 6-6-05 東北大学大学院情報科学研究科 亀山・張山研究室 小松与志也, Tel.: (022)795-7155, Fax.: (022)263-9167, E-mail: ykomatsu@ecei.tohoku.ac.jp

### 1. はじめに

近年,半導体製造技術の進歩により数十億個のトランジスタをチップ上に集積可能になった一方,チップの規模と複雑さの増大により2つの問題が顕在化してきた.一つ目はコストの問題であり,トランジスタの微細化のため工程数が増加し製造コストが増加している.また,集積回路の規模の拡大により,コスト全体に占める設計と検証の割合が増大している.二つ目の問題は性能の問題である.現在ほとんどのデジタル回路はクロック信号に基づいてデータ処理を実行する同期式回路である.同期式回路でより,回路規模の拡大と共にクロックの分配により消費される電力の増加が問題となっている.

一つ目の問題の解決法として,現在フィールドプログラマブルゲートアレイ (FPGA) と呼ばれる LSI が広く使用されている.FPGA は再構成可能な LSI であり,ユーザーは FPGA に回路データを書き込むことで所望の機能を持った

LSI に仕立てることができる. そのため LSI を 設計・製造する必要がなくなり, コストを大幅 に削減することができる.

二つ目の問題に対処するために,近年非同期 式回路が注目されている.非同期式回路におい てデータ処理は処理要求信号と応答信号のやり とりによるハンドシェークによって実行される. そのため非同期式回路ではクロック信号が不要 であり,クロック信号の分配に起因する問題が 発生しない.しかし非同期式回路は同期式回路 と比べ設計が困難であるという問題がある.

非同期式回路の設計を容易にするために,八 ンドシェークコンポーネントベース設計 1) が提 案されている.非同期式回路はハンドシェーク コンポーネントと呼ばれる,データ処理やデー タパス制御機能を持つモジュールを接続するこ とで設計される.そのためハンドシェークコン ポーネントベース設計は理解しやすく,複雑な データ処理を行う回路の設計に適している.

上記の LSI におけるコストと性能の問題を

解決するため,これまでに非同期式 FPGA がいくつか提案されている.コーネル大学  $^{2,3)}$ , $^{2,3)}$ , $^{3}$  Achronix  $^{4)}$ ,東京大学  $^{5)}$  の研究により開発された非同期式 FPGA は,高いスループットを実現するため細粒度パイプラインとなっている.また文献  $^{6,7,8)}$  では,低消費電力であるという非同期式回路の特徴に注目した FPGA アーキテクチャを提案している.しかし,これらの非同期式 FPGA は簡単なデータ転送と処理に特化した単純なハンドシェークのみ実行可能であり,ハンドシェークコンポーネントの実装には適していない.そのため複雑なデータ処理制御を持つアプリケーションを従来の非同期式 FPGA に実装することは困難である.

そこで本研究ではハンドシェークコンポーネントベース設計に適した非同期式 FPGA を提案する.提案 FPGA はハンドシェークコンポーネントを効率的に実装できるため,複雑なデータ処理制御を行うアプリケーションの実装に適する.提案アーキテクチャでは頻繁に使用されるハンドシェークコンポーネントは一つのロジックブロック(LB)で実装できるため,アプリケーションをコンパクトに実装可能である.

# 2. ハンドシェークコンポーネント に基づく非同期式回路設計

#### 2.1 ハンドシェークコンポーネント

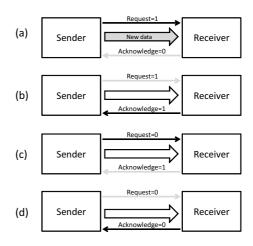

非同期式回路では回路間のデータ転送は処理要求 (Request) 信号と応答 (Acknowledge) 信号のやり取りにより行われる.図1に4相式ハンドシェークを示す.最初に送信側は要求信号を"1"にセットすると同時にデータを送信する.処理が完了すると受信側は応答信号を"1"にセットする.送信側は要求信号を"0"にセットしデータ送信の終了を知らせる.最後に受信側が応答信号を"0"にセットしハンドシェークが終了する.

Fig. 1 4 相式ハンドシェーク.

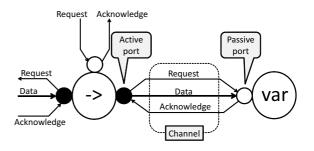

Fig. 2 ハンドシェークコンポーネントとチャネル.

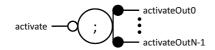

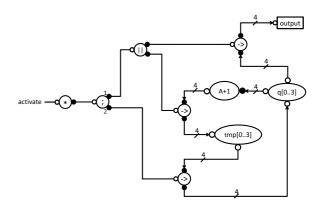

ハンドシェークに基づく非同期式回路の設計 手法として,ハンドシェークコンポーネントによ る設計が提案されている $^{1)}$ .図 $^{2}$ にハンドシェー クコンポーネントの例を示す. 各ハンドシェー クコンポーネントはデータの演算,記憶または データパス制御の機能を持ち,46種類のハンド シェークコンポーネントが定義されている<sup>9)</sup>.そ れぞれのハンドシェークコンポーネントはポー トを持ち、ポート間はチャネルによって接続され る. 複数のハンドシェークコンポーネントがチャ ネルによって接続されることでハンドシェーク サーキットが構成される. ハンドシェークコン ポーネント間の通信は Active port から要求信号 を , Passive port から応答信号を送信することで 行われる.ハンドシェークコンポーネントの例と して, Sequence component の動作を示す. 図3 に Sequence component を示す . Sequence component  $\exists$  activate  $\exists - \vdash \succeq$  activateOut<sub>0</sub>  $b \in$

Fig. 3 Sequence component.

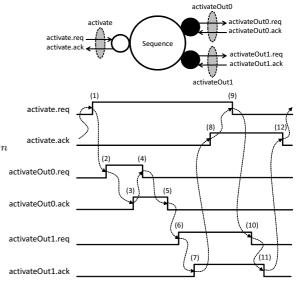

activateOut $_n$  ( $n \ge 1$ )までのポートを持つ . Sequence component は activateOut $_1$  から activateOut $_n$  まで順にハンドシェークを実行し,それらに接続されたハンドシェークコンポーネントを活性化する.これにより Sequence component はハンドシェークサーキットの処理シーケンスを制御する役割を持つ.Sequence component の動作を示す.

- 1) activate.req が "1" にセットされる

- 2) activateOut0.req を "1" にセットする

- 3) activateOut0.ack が"1" にセットされる

- 4) activateOut0.req を "0" にセットする

- 5) activateOut0.ack が"0"にセットされる

- 6) activateOut1.reg を "1" にセットする

- 7) activateOut1.ack が"1"にセットされる

- 8) activate.ack を "1" にセットする

- 9) activate.reg が "0" にセットされる

- 10) activateOut1.reg を "0" にセットする

- 11) activateOut1.ack が"0"にセットされる

- 12) activate.ack を "0" にセットする

上記のようにハンドシェークコンポーネントは複雑なハンドシェークを行う.しかし,各ハンドシェークコンポーネントの機能は単純でありまた複雑な通信はチャネルとして抽象化されるため,ハンドシェークコンポーネントによる非同期式回路設計は理解しやすい.図5にハンドシェークサーキットの例を示す.また,Balsaと呼ばれる回路の高位記述からハンドシェーク

Fig. 4 Sequence component の振る舞い.

Fig. 5 ハンドシェークサーキットの例 (4 ビットカウンタ).

サーキットを生成するツールが公開されている  $^{10)}$  . よって , ハンドシェークコンポーネントベース設計は複雑で大規模な非同期式回路に適している .

# 提案非同期式 FPGA のアーキ テクチャ

#### 3.1 全体のアーキテクチャ

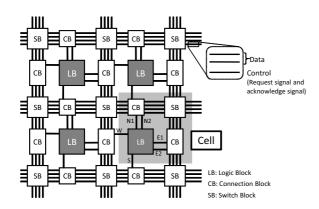

図 6 に提案 FPGA のアーキテクチャを , 図 7 にプログラマブル配線網の構成を示す . 一般的な FPGA と同様に , 提案 FPGA では LB とスイッチブロック (SB) , 2 個のコネクションブロック (CB) からなるセルが縦横に並んだ構造をとっ

Fig. 6 全体のアーキテクチャ.

ている、2個のCBのうち1個はLBのN1,N2,SポートとSBを,1個はE1,E2,WポートとSBを接続する、提案アーキテクチャはBalsa<sup>9)</sup>で定義されている46種類のハンドシェークコンポーネントのうち39種類を実装可能である、規模の大きいハンドシェークコンポーネントは複数個のLBを接続することで実装される、提案アーキテクチャではデータ転送プロトコルに4相2線(Four-Phase Dual-Rail)方式を採用しているため、データ転送のために2本、処理要求信号または応答信号のために1本の合計3本の配線が1ビットの転送のために用意されている、

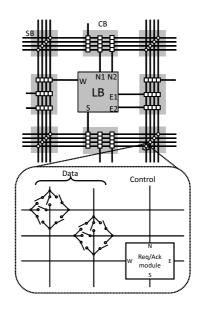

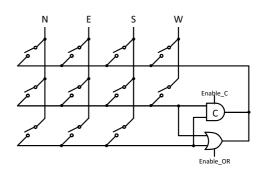

図 7 に示すように , SB はダイヤモンドスイッチと  $\operatorname{Req/Ack}$  モジュールから構成される . 図 8 に  $\operatorname{Req/Ack}$  モジュールの構成を示す .  $\operatorname{Req/Ack}$  モジュールはスイッチと  $\operatorname{OR}$  ゲート , マラーの  $\operatorname{C}$  素子  $\operatorname{SP}$  から構成される .  $\operatorname{Req/Ack}$  モジュールはトラックの処理要求信号または応答信号を別のトラックに転送する . また ,  $\operatorname{Req/Ack}$  モジュールは  $\operatorname{2}$  方向から入力された処理要求信号または応答信号を  $\operatorname{C}$  素子または  $\operatorname{OR}$  ゲートで統合する役割を持つ .

#### 3.2 ロジックブロックの構成

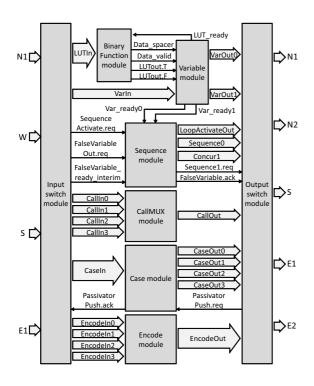

図 9 に提案 FPGA の LB の構成を示す . LB は BinaryFunction モジュール , Variable モジュール , Sequence モジュール , CallMUX モジュール , Case モジュール , Encode モジュールとそ

Fig. 7 LB の周囲のプログラマブル配線網.

Fig. 8 Reg/Ack モジュールの構成.

れらの入出力と CB を接続する InputSwitch モジュール , OutputSwitch モジュールから構成される . 表 1 にモジュールとそれが実装するハンドシェークコンポーネントを示す . 一つのモジュールを数種類のハンドシェークコンポーネントが共用しているため , 提案アーキテクチャでは小面積で 39 種類のハンドシェークコンポーネントをサポートしている .

#### 4. 評価

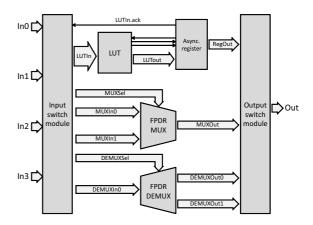

提案 FPGA を e-Shuttle 社の 65nmCMOS プロセスで実装し,電源電圧 1.2V,回路温度 85℃の条件の下 HSPICE シミュレーションにより評価した.比較のため同条件で従来型非同期式FPGA の評価も行った.図 10 に示すように,従

Fig. 9 LB の構成.

来型非同期式 FPGA の LB は主にルックアップ テーブル (LUT) と非同期式レジスタ , FPDR マルチプレクサ・デマルチプレクサから構成される  $^{11)}$  .

表 2 にセルあたりのトランジスタ数を示す. 提案アーキテクチャでは LB 内にハンドシェークコンポーネント実装のためのモジュールを持つため,従来型アーキテクチャと比較してトランジスタ数が 62%増加した.

次に , 4bit カウンタ , 条件分岐付き 4 ビットカ

Table 1 LB 内のモジュールと実装可能なハンドシェークコンポーネント.

| Module                                    | Handshake component                                                                                                                                      |  |  |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Variable                                  | BuiltinVariable, Variable                                                                                                                                |  |  |

| Sequence                                  | Concur, Loop, Sequence, While                                                                                                                            |  |  |

| CallMUX                                   | Call, CallMUX, Continue, ContinuePush                                                                                                                    |  |  |

| Case                                      | CallDEMUX, Case,<br>CaseFetch, DecisionWait,<br>PassivatorPush, SynchPush                                                                                |  |  |

| Encode                                    | Encode                                                                                                                                                   |  |  |

| BinaryFunction and Variable               | BinaryFunc, BinaryFuncConstR, UnaryFunc                                                                                                                  |  |  |

| Variable and<br>Sequence                  | FalseVariable,<br>ActiveEagerFalseVariable,<br>PassiveEagerFalseVariable                                                                                 |  |  |

| Programmable<br>Interconnect<br>resources | Adapt, Combine, CombineEqual,<br>Constant, Fetch, Fork, ForkPush,<br>Halt, HaltPush, Passivator, Slice, Split,<br>SplitEqual, Synch, SynchPull, WireFork |  |  |

Fig. 10 従来型非同期式 FPGA の LB.

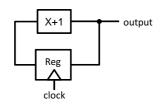

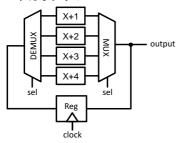

ウンタを非同期  ${

m FPGA}$  上に実装した場合の評価 結果を示す.図 11 に等価な同期式回路を示す.表 3 にトランジスタ数の比較を示す.4 bit カウンタではセル数は 21%減少したものの,トランジスタ数は 27%増加した.一方条件分岐付き 4 bit カウンタではセル数とトランジスタ数はそれぞれ 45% と 11%減少した.これはハンドシェークコンポーネントベース設計では条件分岐のような制御を含むアプリケーションを効率的に設計できるためである.

表 4 にデータの処理 1 回あたりの消費エネルギーの比較を示す . 4bit カウンタでは従来型アーキテクチャに比べ 9% , 条件分岐付き 4bit カウンタでは 27%消費エネルギーが削減された . ハンドシェークコンポーネントベース設計は複雑な制御を含むアプリケーションでより有利である .

表 5 にデータの出力スループットの比較を示す.4bit カウンタでは従来型アーキテクチャと比較して 51%,条件分岐付き 4bit カウンタでは41%スループットが低下した.これは,従来型アーキテクチャと比較して提案アーキテクチャはセル間のハンドシェークが複雑であるためである.

#### 5. おわりに

本論文ではハンドシェークコンポーネントベース設計に適した非同期式 FPGA を提案した.ハ

Table 2 1 セルあたりのトランジスタ数とその内訳.

|            | Conventional architecture | Proposed architecture |

|------------|---------------------------|-----------------------|

| Cell       | 2401                      | 3893                  |

| LB         | 589                       | 1255                  |

| SB and CBs | 1812                      | 2638                  |

(a) 同期式回路における 4 ビットカウンタ.

(b) 同期式回路における条件分岐付き 4 ビットカウンタ.

Fig. 11 提案アーキテクチャの評価回路と同等の機能を持つ同期式回路.

ンドシェークコンポーネントベース設計は複雑な 制御を含むアプリケーションに適しているため, 提案アーキテクチャは従来型非同期式 FPGA アーキテクチャに比べ大規模なアプリケーショ ンの実装に有利である.

今後の課題として、従来型アーキテクチャと今回提案したアーキテクチャのハイブリッドアーキテクチャが考えられる。従来型アーキテクチャはセルが単純でコンパクトでありスループットが高い一方、提案アーキテクチャは複雑な制御を含むアプリケーションを効率的に実装できる。よってハイブリッドアーキテクチャではデータパスの部分はシンプルな従来型アーキテクチャを、アプリケーションの制御部は提案アーキテクチャを用いることで低消費電力、高スループットかつ小面積な実装が可能となる。

Table 3 トランジスタ数の評価結果. (a) 4 ビットカウンタの評価結果.

|                       | Conventional architecture | Proposed architecture |

|-----------------------|---------------------------|-----------------------|

| Number of cells       | 14                        | 11                    |

| Number of transistors | 33614                     | 42823                 |

#### (b) 条件分岐付き 4 ビットカウンタの評価結果.

|                       | Conventional architecture | Proposed architecture |

|-----------------------|---------------------------|-----------------------|

| Number of cells       | 53                        | 29                    |

| Number of transistors | 127253                    | 112897                |

Table 4

1 データ処理あたりの消費エネルギー

の評価結果

.

|                                            | Conventional architecture | Proposed architecture |

|--------------------------------------------|---------------------------|-----------------------|

| 4-bit counter [pJ]                         | 5.04                      | 4.57                  |

| 4-bit counter with conditional branch [pJ] | 13.49                     | 9.88                  |

### 謝辞

This work is supported by VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with STARC, e-Shuttle, Inc., Fujitsu Ltd., Cadence Design Systems Inc. and Synopsys Inc. 本研究は東京大学大規模集積システム設計教育研究センターを通し,株式会社半導体理工学研究センター,(株) イー・シャトル,富士通株式会社,日本ケイデンス株式会社およびシノプシス株式会社の協力で行われたものである.また本研究は JSPS 科研費 25・5513 の助成を受けたものである.

Table 5 スループットの評価結果.

|                                                          | Conventional architecture | Proposed architecture |

|----------------------------------------------------------|---------------------------|-----------------------|

| 4-bit counter<br>[M operations/sec]                      | 162.50                    | 79.06                 |

| 4-bit counter with conditional branch [M operations/sec] | 85.70                     | 50.28                 |

## 参考文献

- K. van Berkel, J. Kessels, M. Roncken, R. Saeijs, and F. Schalij, "The VLSIprogramming language Tangram and its translation into handshake circuits," Proc. EDAC, pp.384–389, 1991.

- J. Teifel and R. Manohar, "An asynchronous dataflow FPGA architecture," IEEE Transactions on Computers, vol.53, no.11, pp.1376– 1392, 2004.

- 3) R. Manohar, "Reconfigurable Asynchronous Logic," Proceedings of IEEE Custom Integrated Circuits Conference, pp.13–20, Sept. 2006.

- 4) Achronix Semiconductor Corporation, "Introduction to Achronix FPGAs", Aug 2008.

- 5) B. Devlin, M. Ikeda, and K. Asada, "A 65 nm gate-level pipelined self-synchronous fpga for high performance and variation robust operation," Solid-State Circuits, IEEE Journal of, vol.46, no.11, pp.2500–2513, Nov.

- 6) M. Hariyama, S. Ishihara, and M. Kameyama, "Evaluation of a Field-Programmable VLSI Based on an Asynchronous Bit- Serial Architecture," IEICE Trans. Electron, vol.E91-C, no.9, pp.1419–1426, 2008.

- 7) S. Ishihara, Y. Komatsu, M. Hariyama, and M. Kameyama, "An Asynchronous Field-Programmable VLSI Using LEDR/4-Phase-Dual-Rail Protocol Converters," Proceedings of The International Conference on Engineering of Reconfigurable Systems and Algorithms (ERSA), Las Vegas(USA), pp.145–150, Jul 2009.

- 8) M. Hariyama, S. Ishihara, and M. Kameyama, "A Low-Power Field-Programmable VLSI Based on a Fine-Grained Power-Gating Scheme," Proceedings of IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Knoxville(USA), pp.430– 433, Aug 2008.

- D. Edwards, A. Bardsley, L. Janin, L. Plana, and W. Toms, "Balsa: A Tutorial Guide," May 2006.

- A. Bardsley, "Implementing Balsa Handshake Circuits," 2000.

- J. Sparsø and S. Furber, "Principles of Asynchronous Circuit Design: A Systems Perspective," 2001.